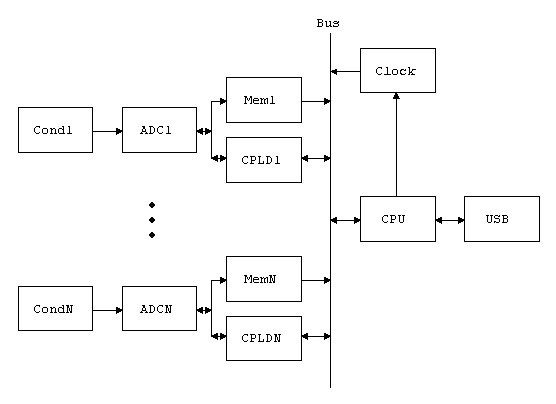

Schema a blocchi

Dopotutto anche un

oscilloscopio digitale (almeno, quello che costruirò io) ha un'architettura

piuttosto semplice:

La struttura è modulare.

I blocchi contrassegnati dai numeri 1...N costituiscono i moduli degli eventuali

canali dell'oscilloscopio. Ogni modulo è collegato su un bus comune

supervisionato da una CPU, che si occupa anche dell'I/O da e verso il PC.

Segue una descrizione dei blocchi che costituiscono ciascun canale, con una possibile scelta dei dispositivi

elettronici a disposizione per implementarli.

- Cond (blocco di

condizionamento): adatta il segnale in ingresso in modo che esso possa

essere gestito dall'ADC. Svolge diverse funzioni: protezione da spikes o

sovratensioni; amplificazione o attenuazione del segnale; filtraggio delle

componenti del segnale che violerebbero il teorema di Nyquist. Per

amplificare/attenuare un segnale acquisito a otto bit è inutile usare un

costoso PGA con controllo digitale; sono sufficienti pochi operazionali ad

alta velocità (come l'AD8057

della Analog Devices, 1.61 € da RS), switch analogici e resistenze di

precisione. Per quanto riguarda il filtraggio, dopo qualche ricerca ho

concluso che è molto difficile riuscire a implementare un filtro programmabile a basso

prezzo e con componenti facilmente reperibili; per ora credo che mi

limiterò a filtrare le componenti a frequenza superiore a quella massima

dell'ADC, e a verificare i risultati.

- ADC: è il

convertitore analogico-digitale, il cuore dell'oscilloscopio. RS dispone di

due modelli interessanti: l'ADS830

della Burr-Brown (60 MSPS, 7.32 €) e il TSA0801

della ST (40 MSPS, 5.75 €). In linea di principio ho sempre trovato i

dispositivi della Burr-Brown all'altezza della situazione, e 10 MHz in più

credo che valgano due euro scarsi in più. Inoltre l'ADS830 ha un package

molto più semplice da gestire (un SO20) ed è pin-to-pin compatibile con il

suo fratello maggiore a 80 MSPS, l'ADS831. Sono quindi orientato verso il

prodotto della BB.

- Mem: è il

buffer di ciascun canale. La memoria viene utilizzata come buffer circolare

e viene continuamente riempita dai nuovi campioni acquisiti dall'ADC, in

modo che in ogni istante siano disponibili gli ultimi N campioni (con N

dimensione della memoria). Fortunatamente le SRAM non costano più un

patrimonio come una volta, così ad esempio una CY7C199-15

della Cypress (32k*8, 15 ns) costa appena 3.42 € da RS. E 32768 campioni

sono più che sufficienti per i nostri scopi; anzi, probabilmente la banda

messa a nostra disposizione dal bus USB ci obbligherà in certi casi a

utilizzarne meno!

- CPLD: è la

logica programmabile che si occupa dei compiti "ausiliari" (come

il pilotaggio del guadagno del PGA), ma la sua

funzione principale è quella di regolare il riempimento della SRAM. In

linea di principio questa sarebbe un'operazione piuttosto semplice; ciò che

complica tutto è la gestione del trigger, che deve necessariamente

essere svolta dalla CPLD (ne parlerò nel prossimo capitolo). Anche le CPLD

hanno ormai dei prezzi abbastanza affrontabili; ad esempio una XC9572XL-10TQ100

(72 macrocelle, 100 MHz, apparentemente sufficiente per il nostro design) costa

7.82 € da RS.

Supponendo di utilizzare

i dispositivi ipotizzati e facendo una stima per largo eccesso risulta un costo

di 25 € per canale, che mi sembra molto buono.

Segue ora la descrizione dei blocchi rimanenti del sistema, che sono comuni per

tutti i canali.

- Clock: è il

generatore della frequenza di campionamento di tutti i canali ADC (sarebbe

stato interessante permettere la selezione della frequenza per ogni singolo

canale, ma per ora ho deciso di ignorare questa possibilità).

- CPU: il

microprocessore/controllore principale. Esso sostanzialmente dovrà

limitarsi a gestire la comunicazione sul bus USB e trasferire in modo

abbastanza "stupido" (e lentamente, alla frequenza di

aggiornamento del display) i dati dalle memorie di ciascun canale verso il

PC; i compiti critici in termini di velocità sono svolti dalle CPLD, per

cui non è necessario impiegare una CPU particolarmente potente. Ho scelto

il PIC16F877 per una serie di vantaggi che illustrerò nel capitolo

dedicato alla scheda madre.

- USB:

l'interfaccia di comunicazione USB. Con i dispositivi di FTDI

tutta la gestione "complicata" del protocollo USB (endpoint,

descrittori e in generale tutto il protocollo a basso livello) viene

nascosta dietro a un puro e semplice buffer FIFO, una pipe bidirezionale con

due flag che segnalano quando il buffer in trasmissione è vuoto e quello in

ricezione è pieno. In particolare il FT8U245AM

è un dispositivo con interfaccia parallela a otto bit che sembra fatto al

caso nostro. Questo è uno dei pochi componenti che RS non ha, ma per

fortuna esistono diversi metodi per reperirlo, ad esempio su Elettroshop

o su questo shop online svedese (un sentito ringraziamento a Gabriele Bellini per

entrambe le segnalazioni!).

Indice

(precedente) Principio di funzionamento di base di un oscilloscopio

(prossimo) Il firmware della CPLD

|